スルーホール穴埋め

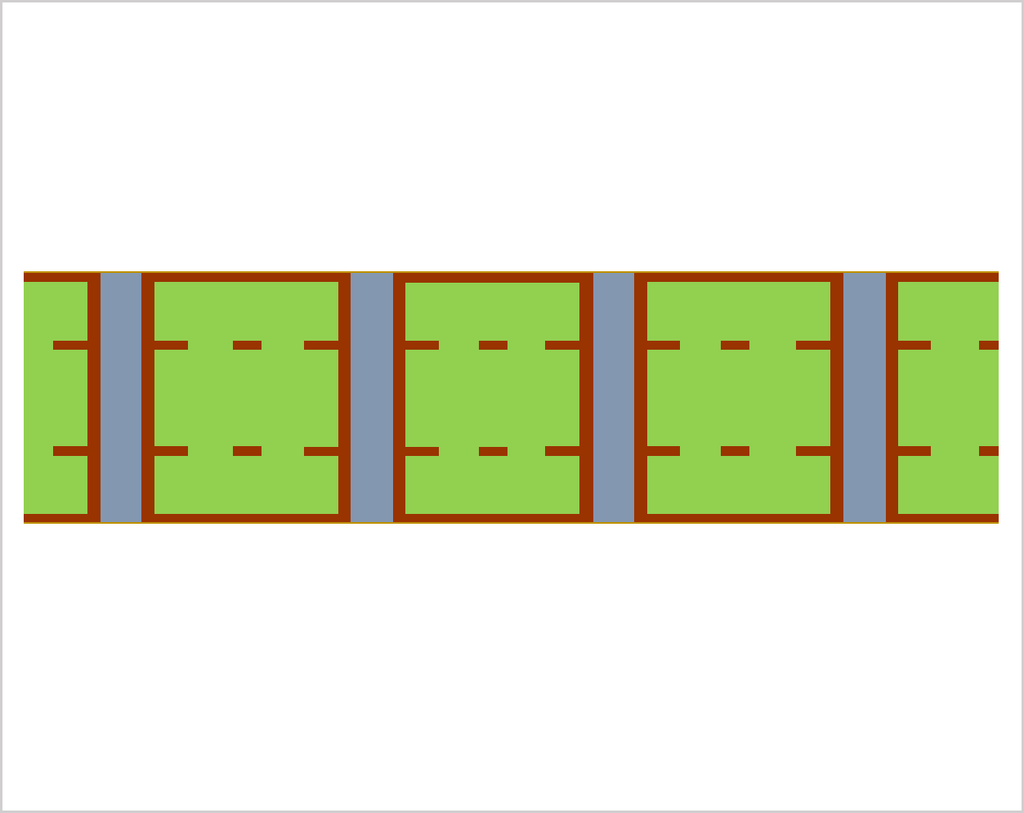

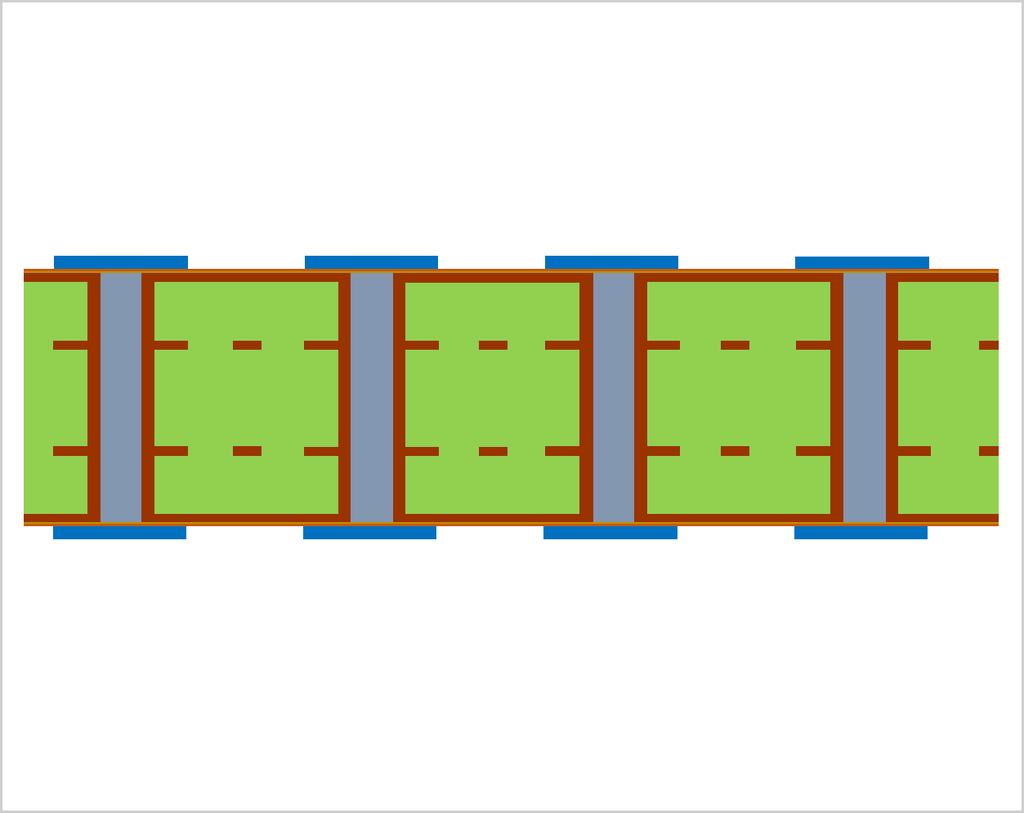

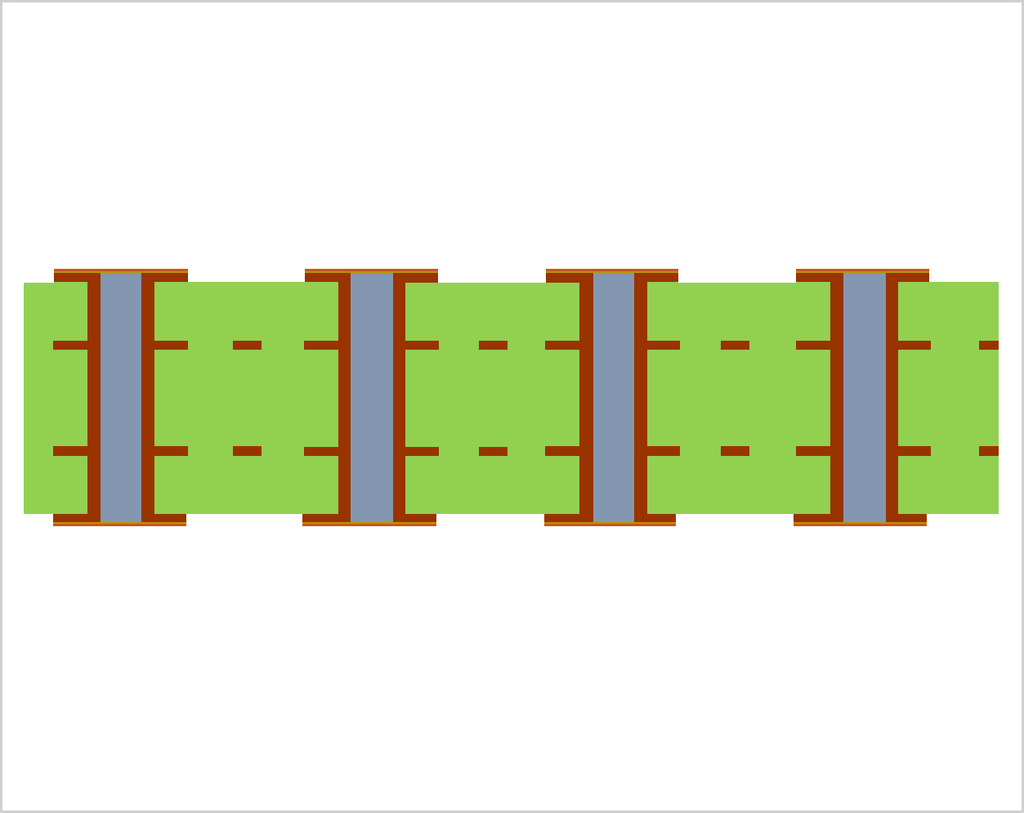

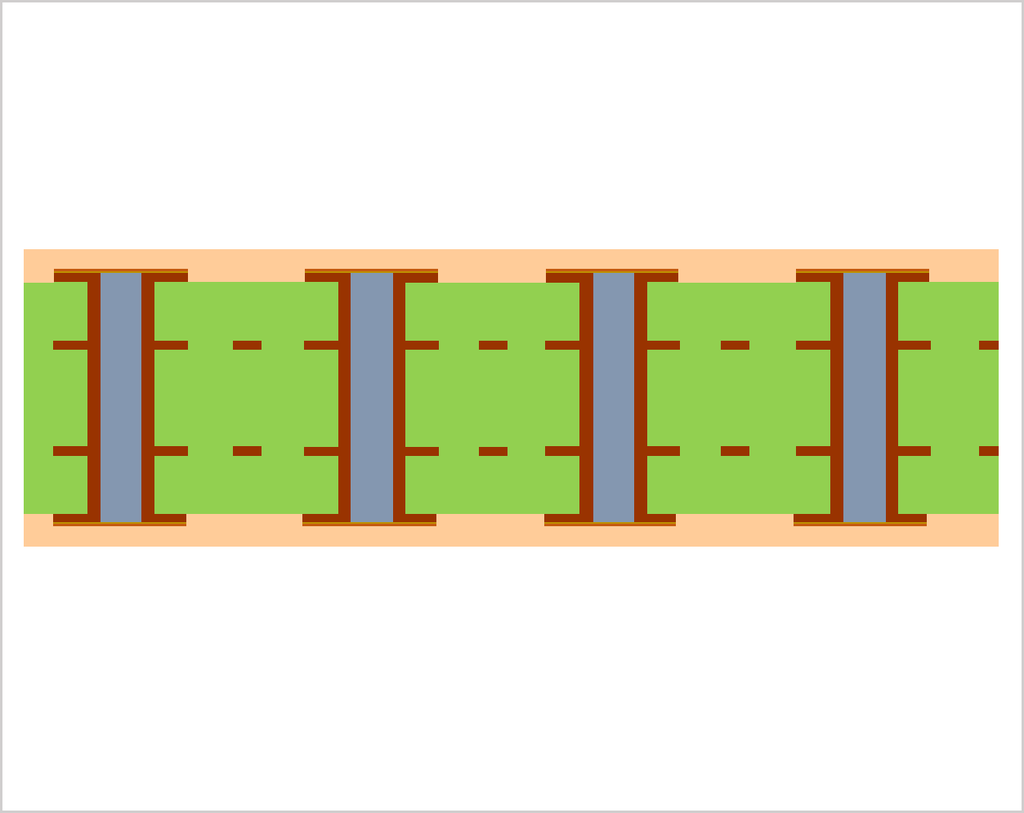

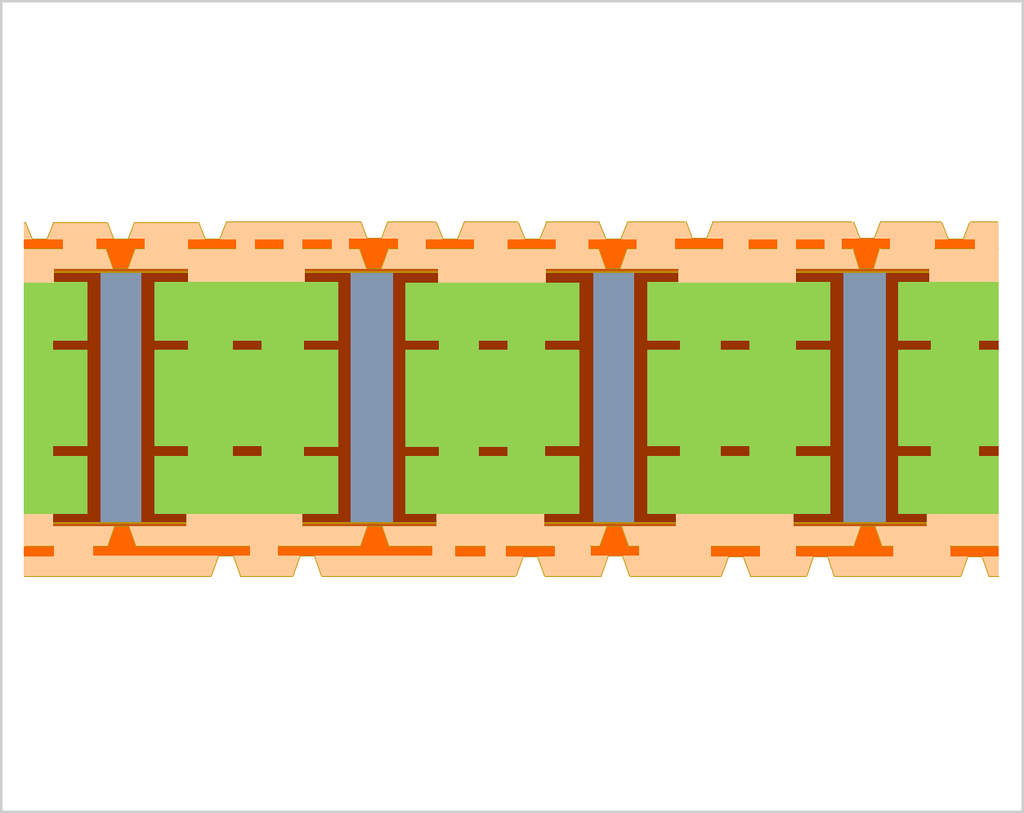

6層板、4層板などの一般的な多層プリント配線板(プリント基板)をコアに用います。ここでは最外層をスルーホールめっきした状態の4層板を出発材料として解説します。なお、多層プリント配線板の製造方法は、当サイトの「多層プリント配線板製造に貢献するOKUNOのプロセス」をご覧ください。

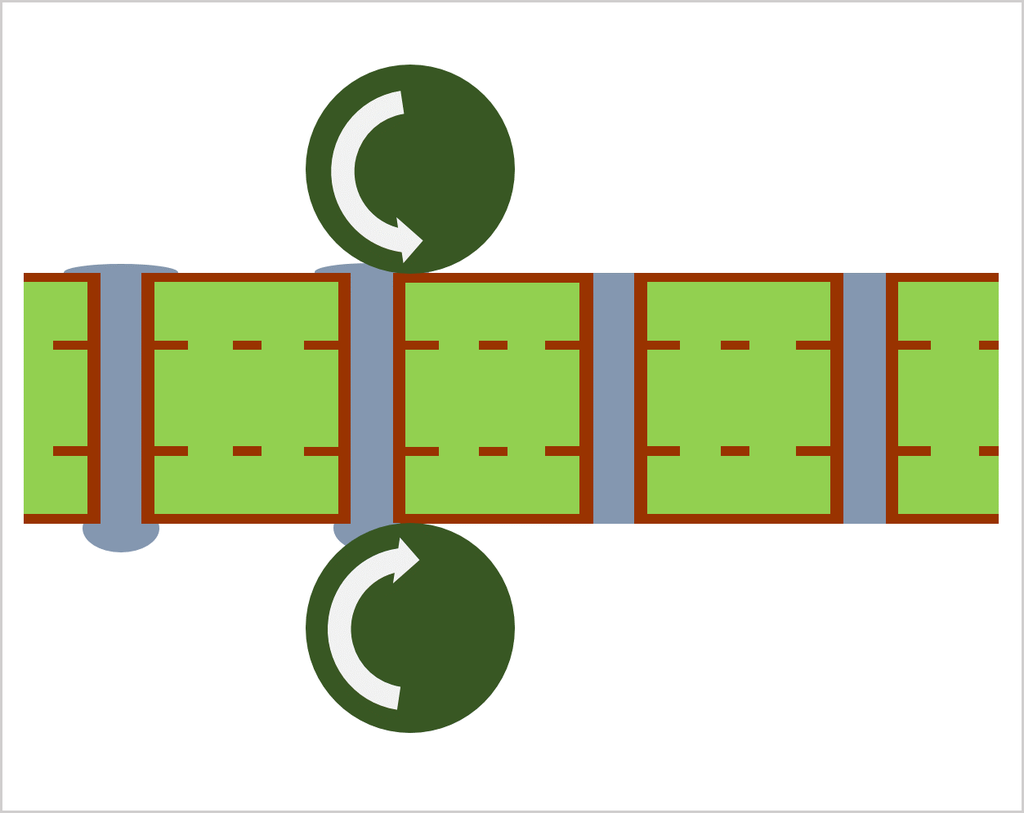

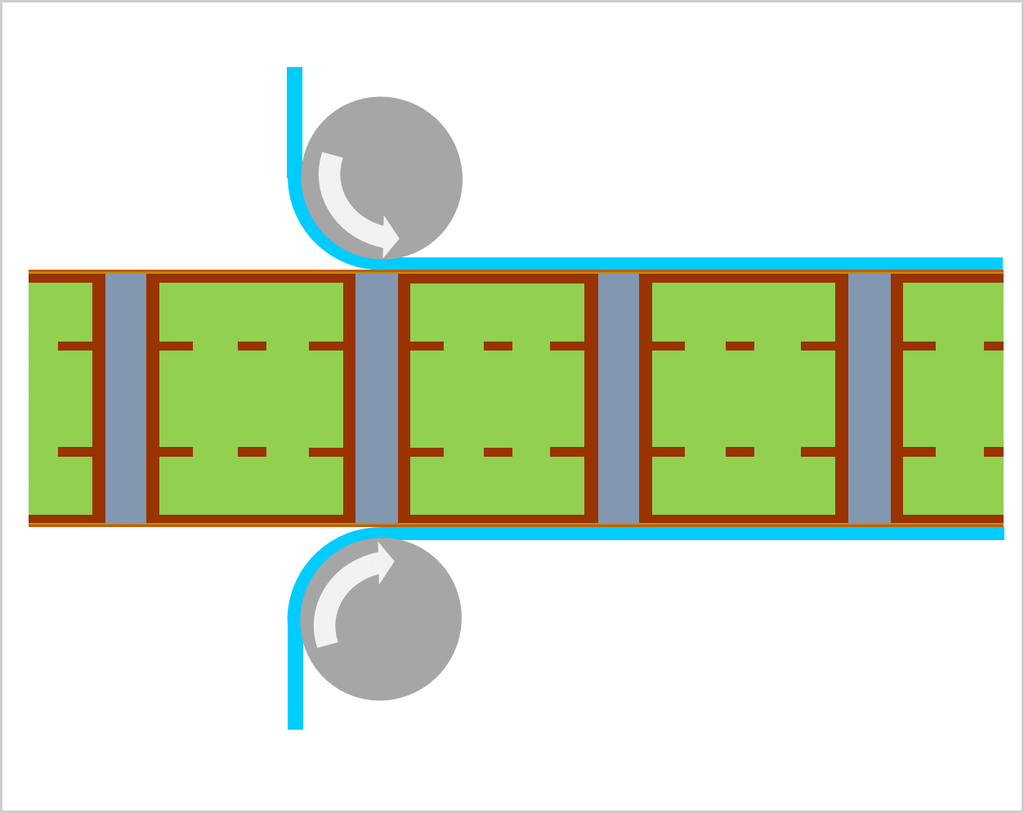

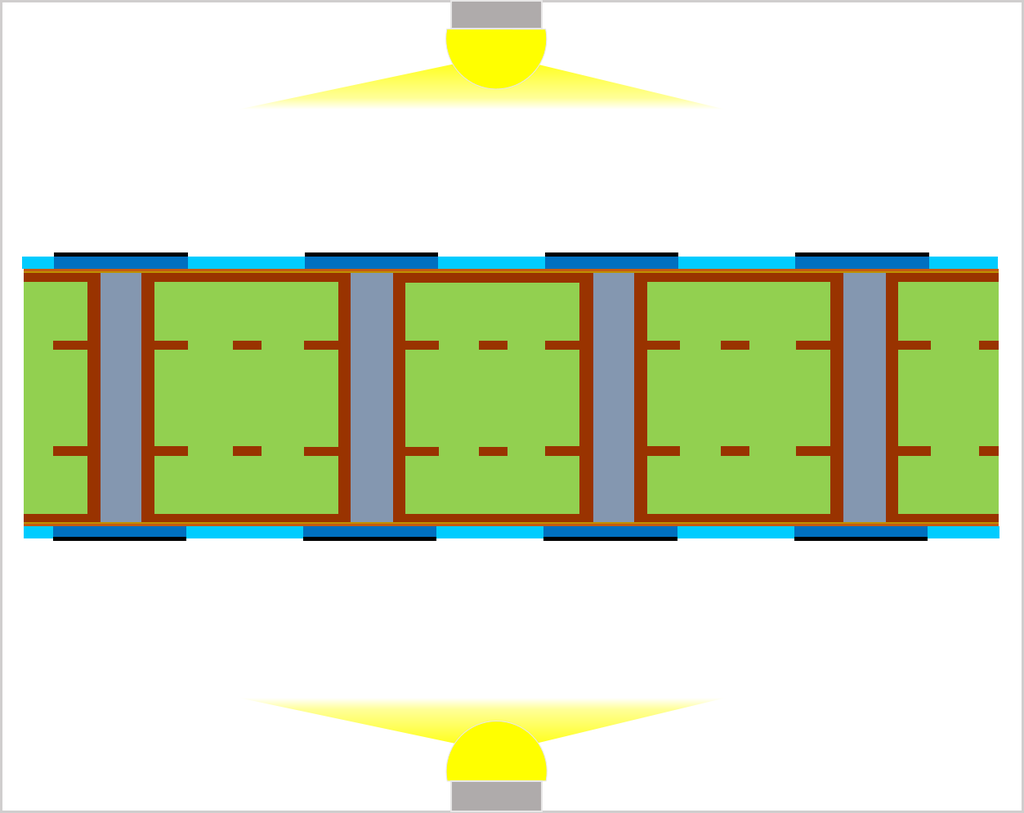

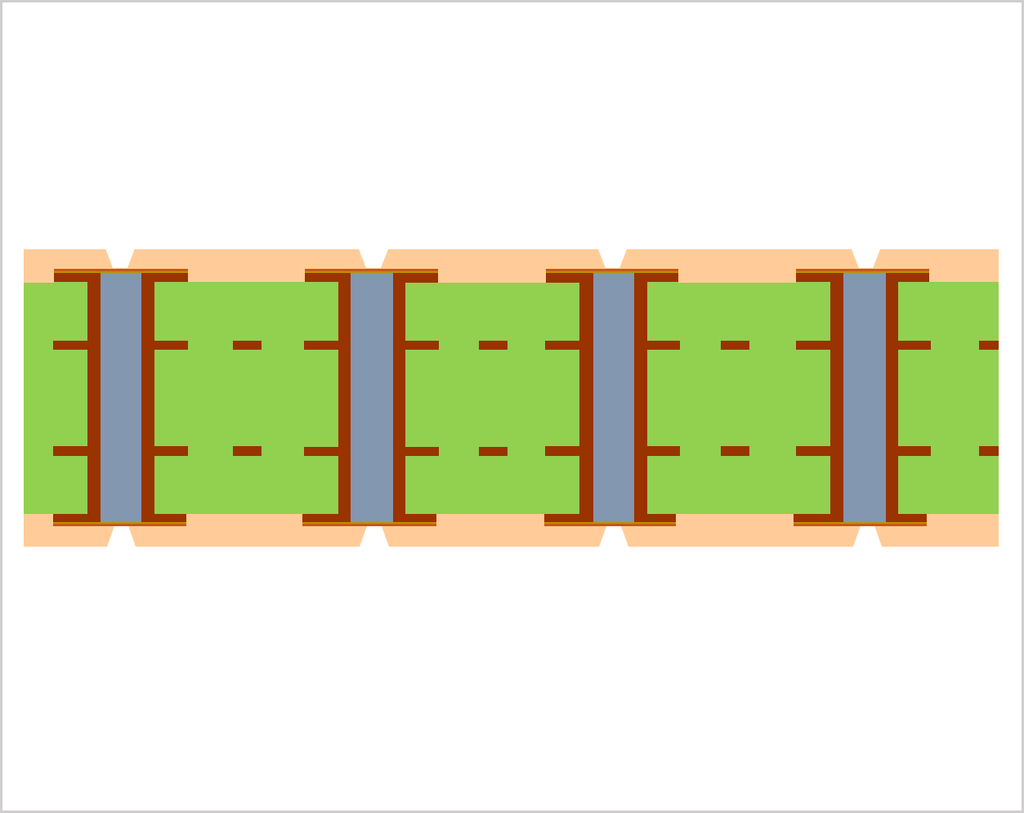

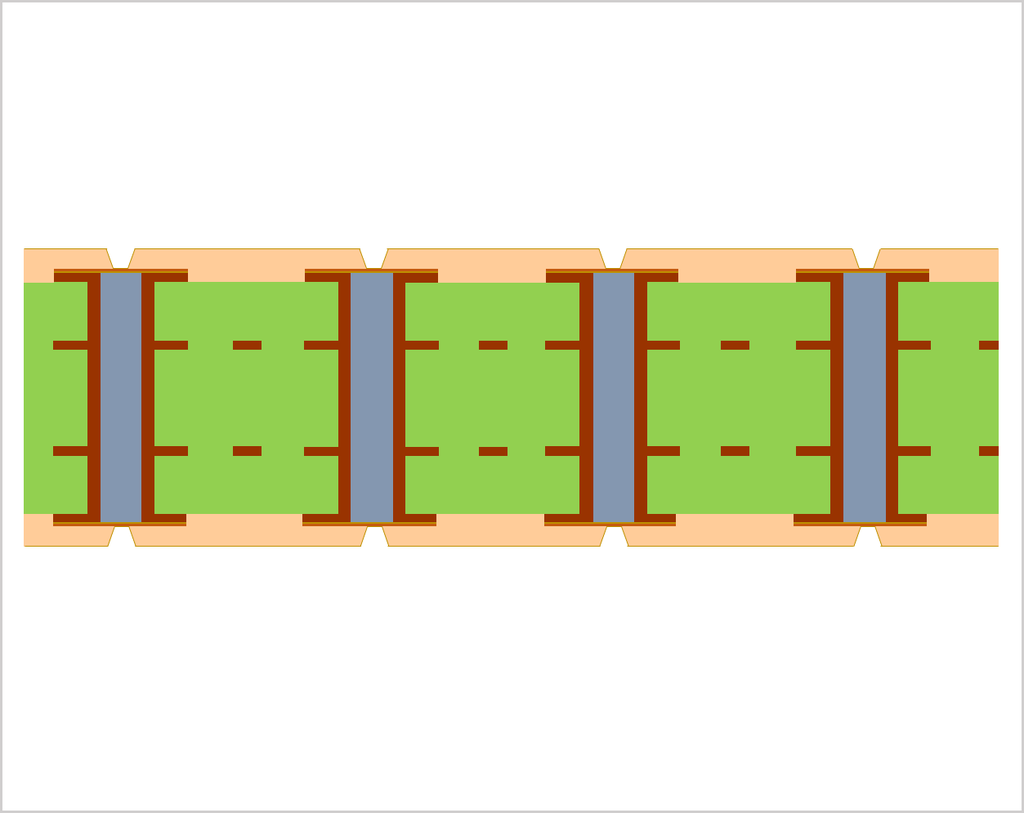

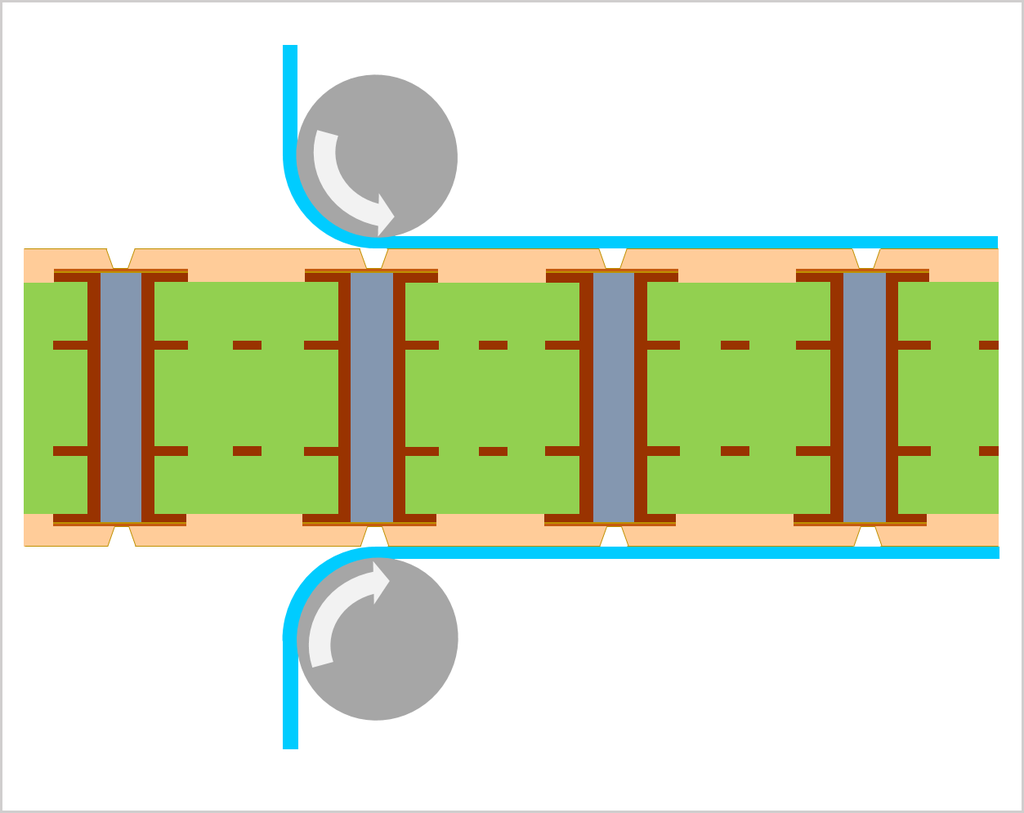

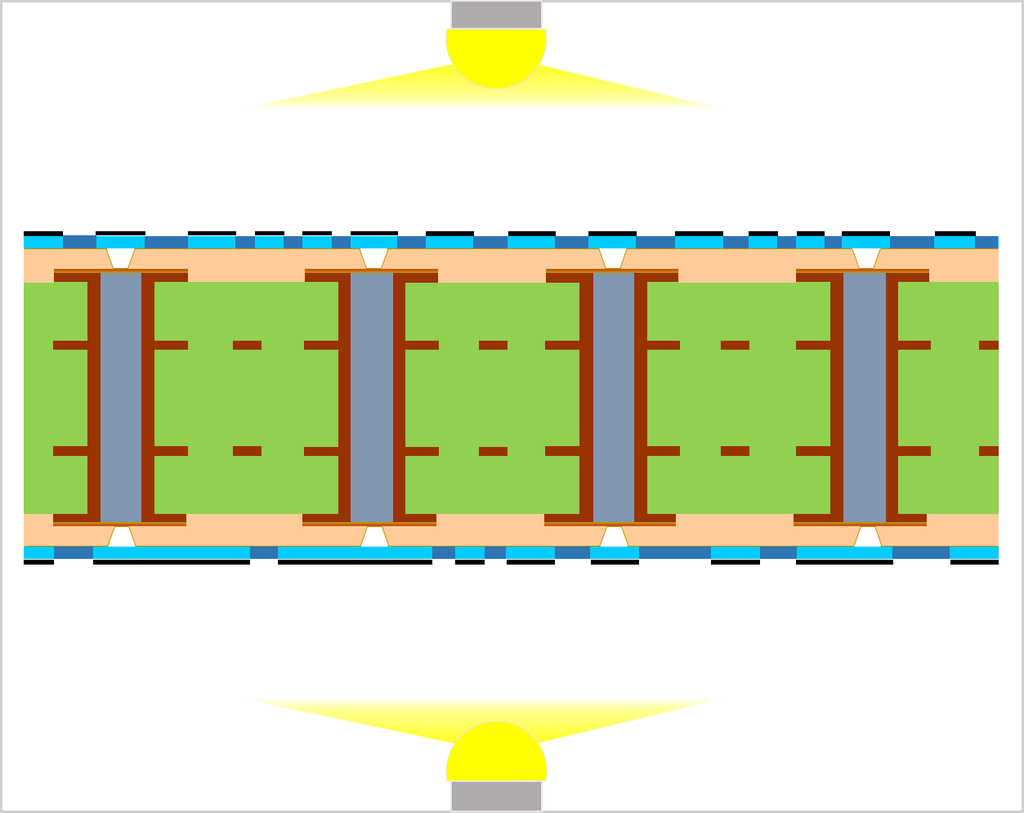

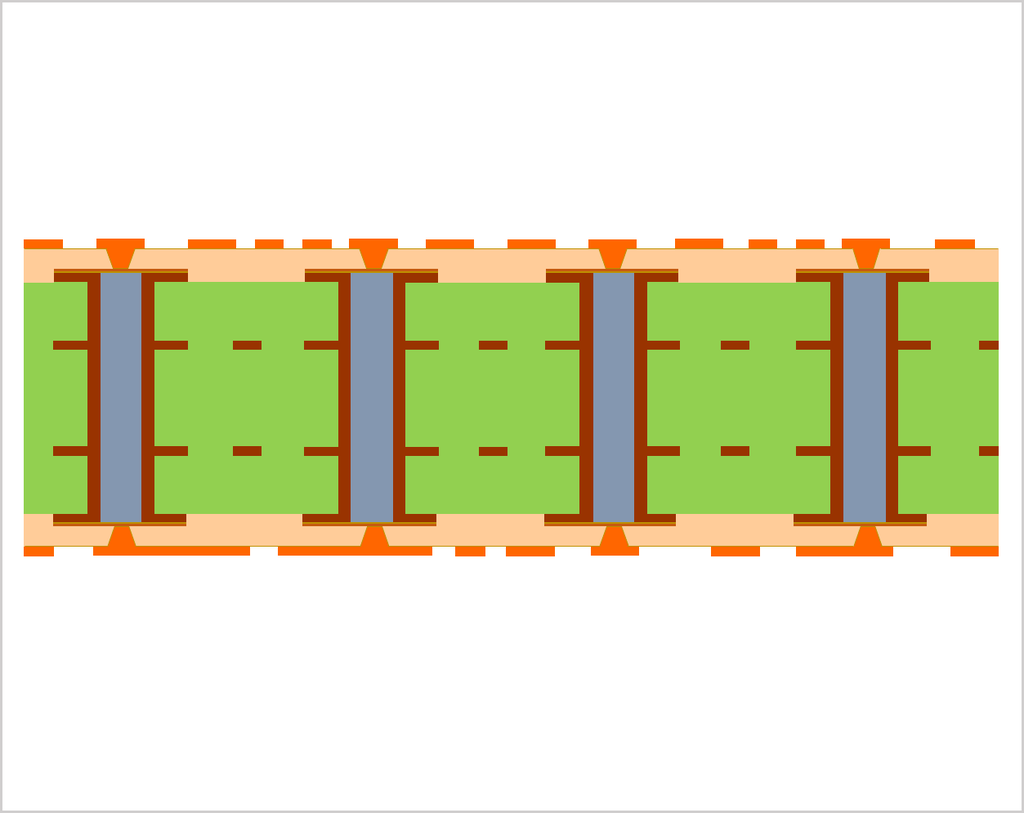

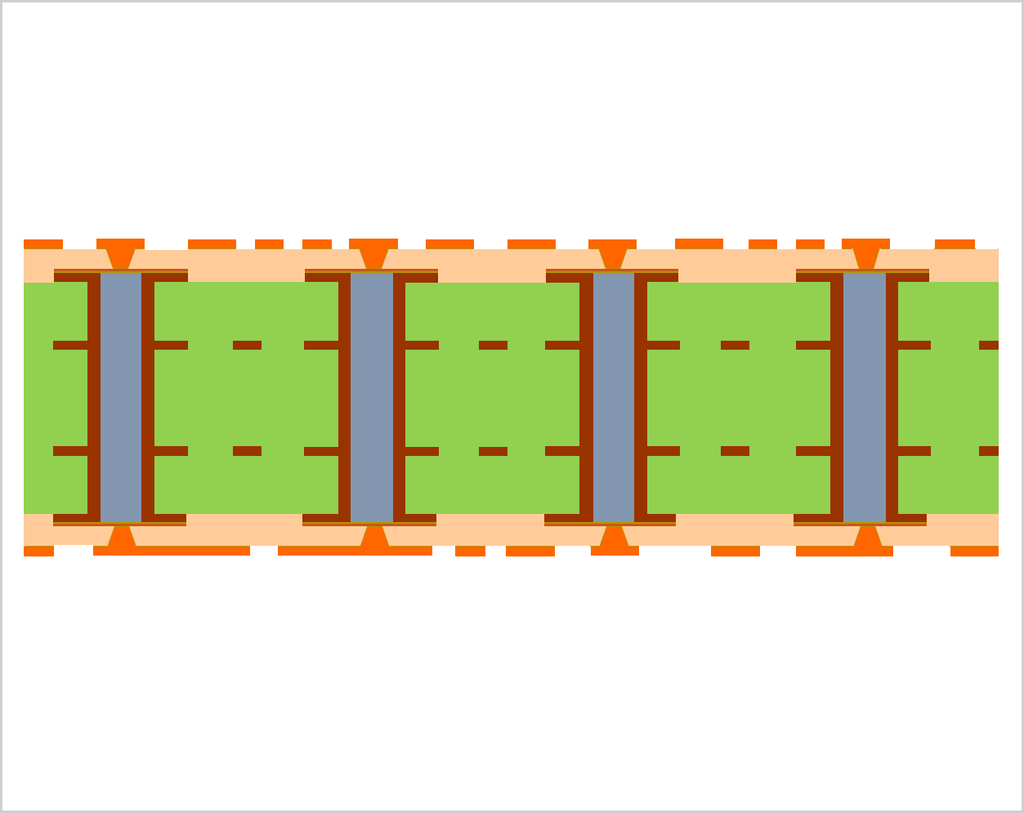

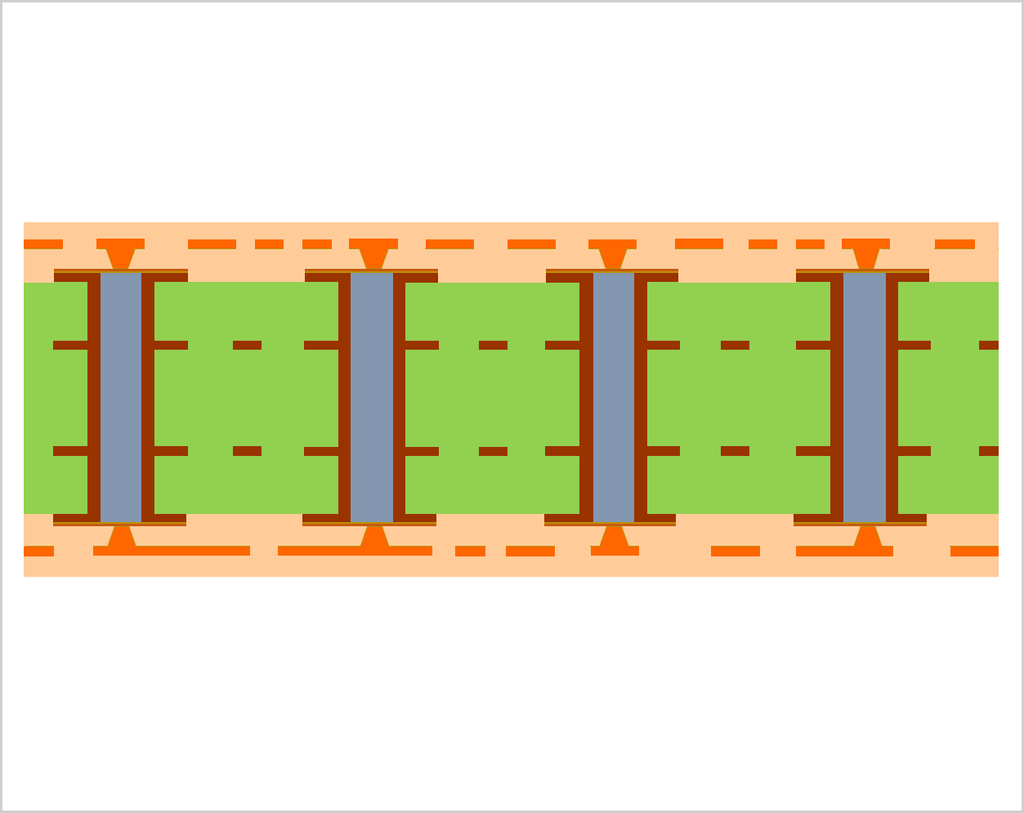

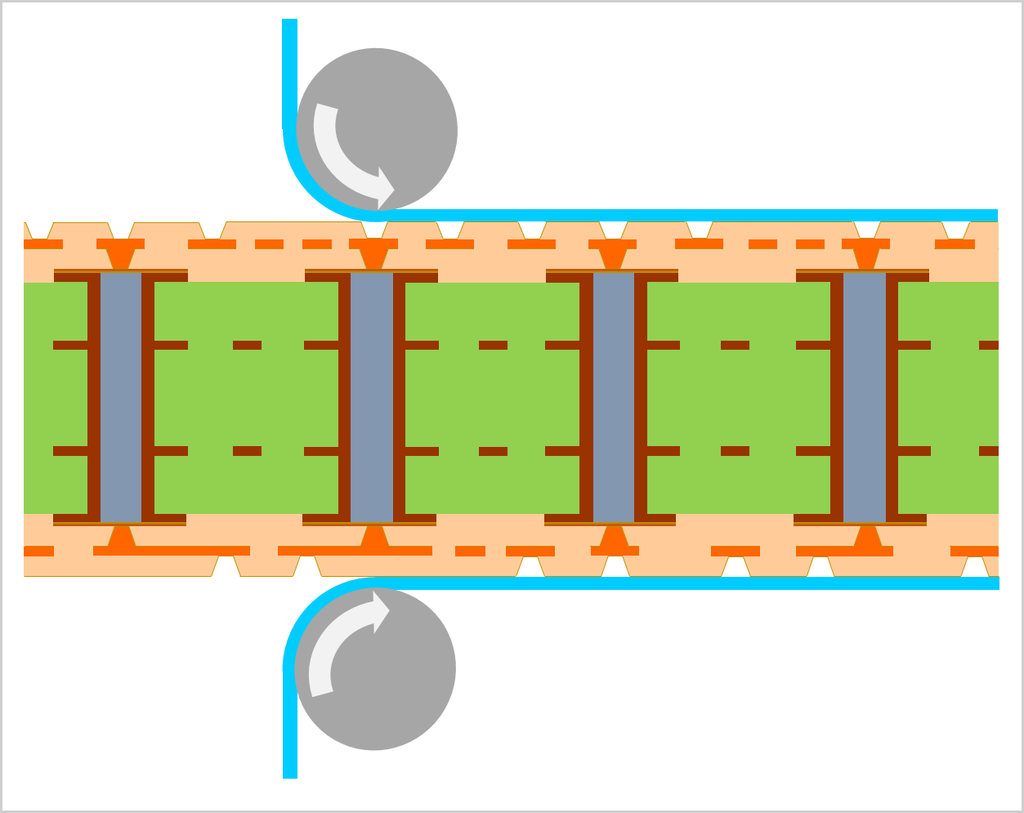

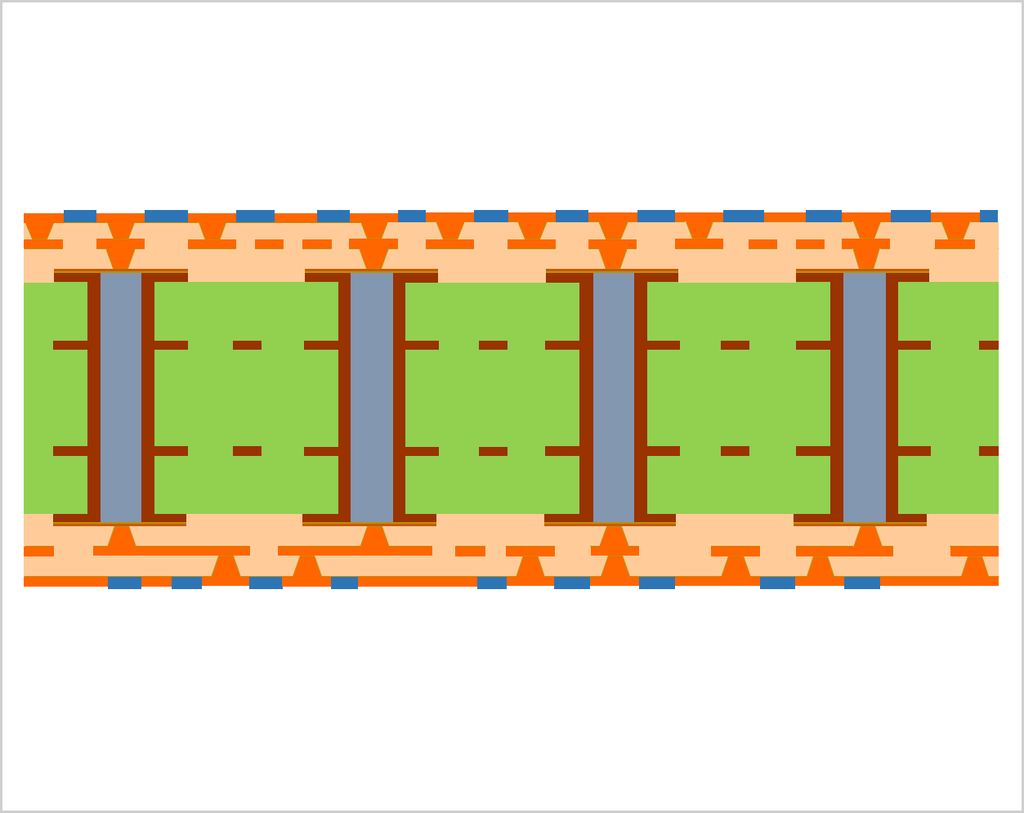

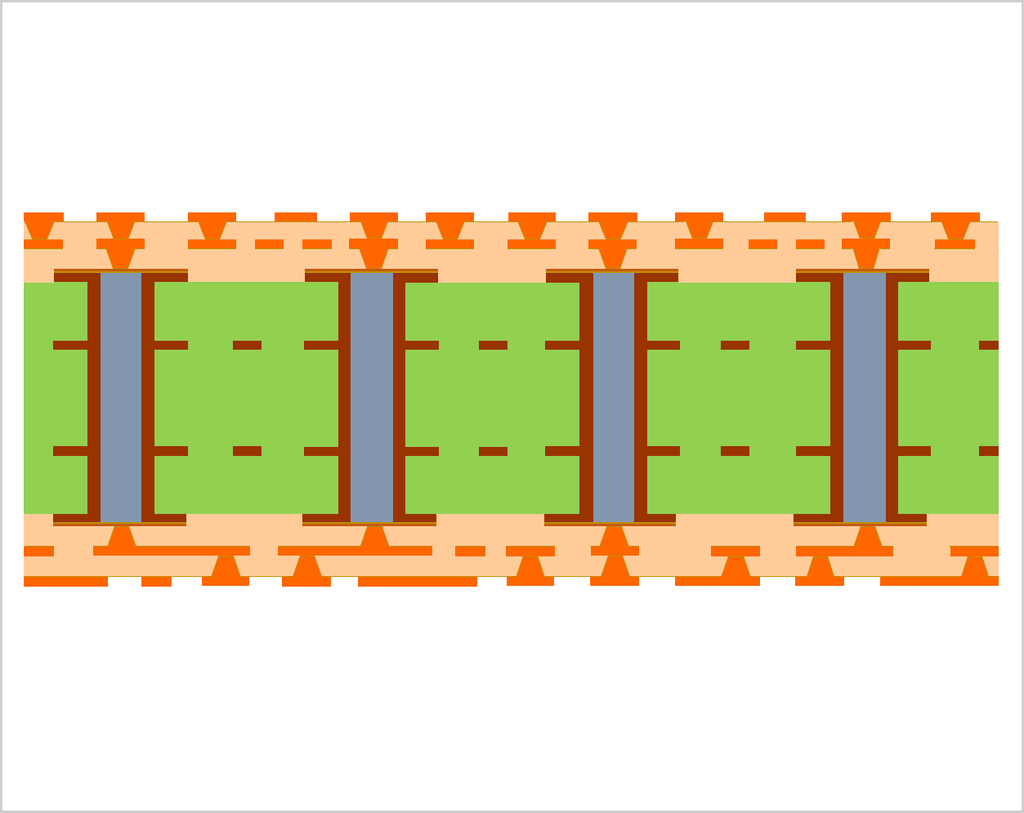

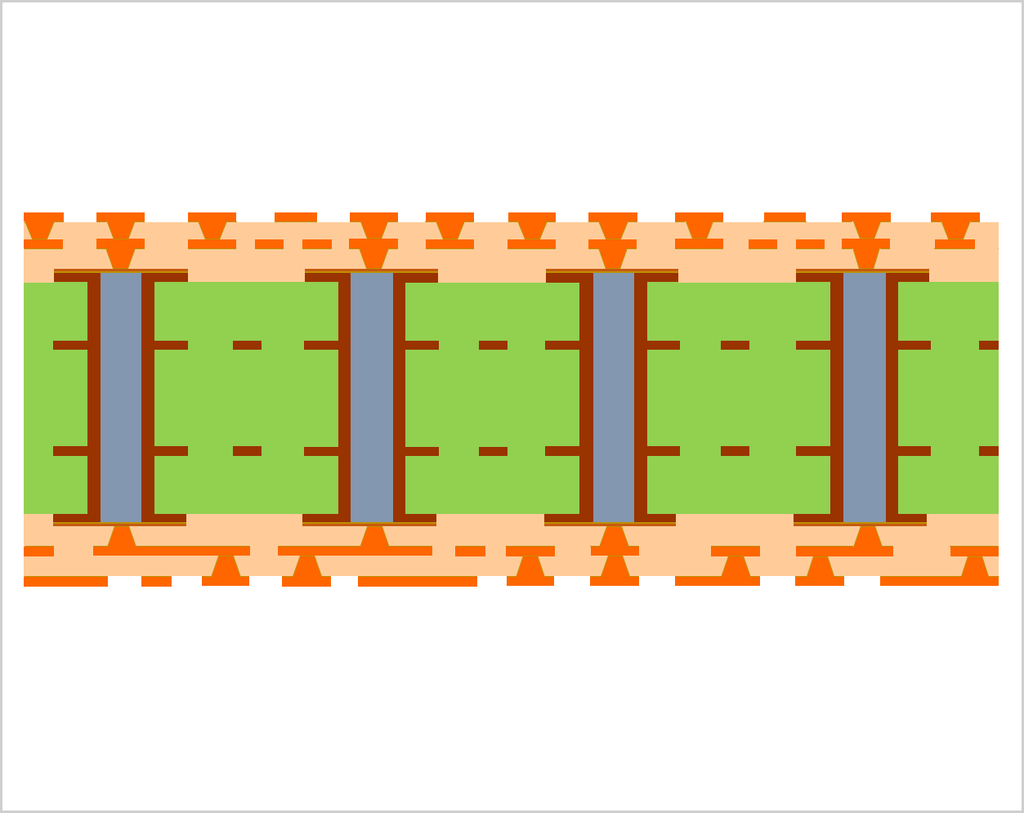

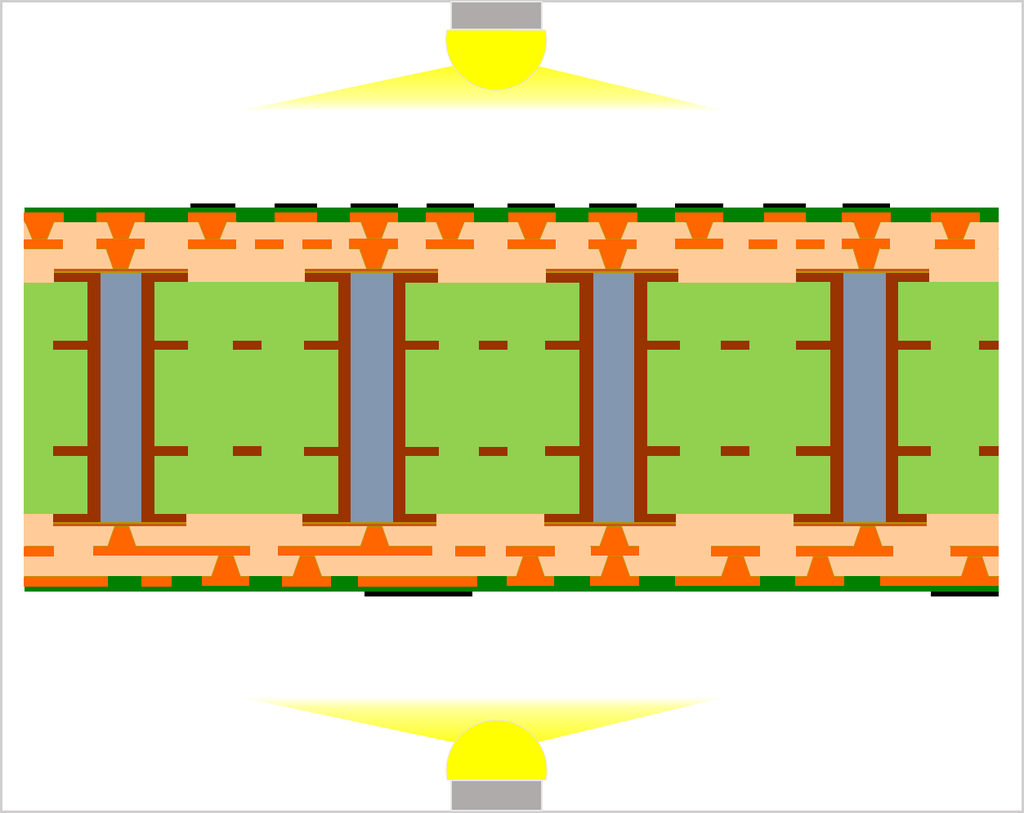

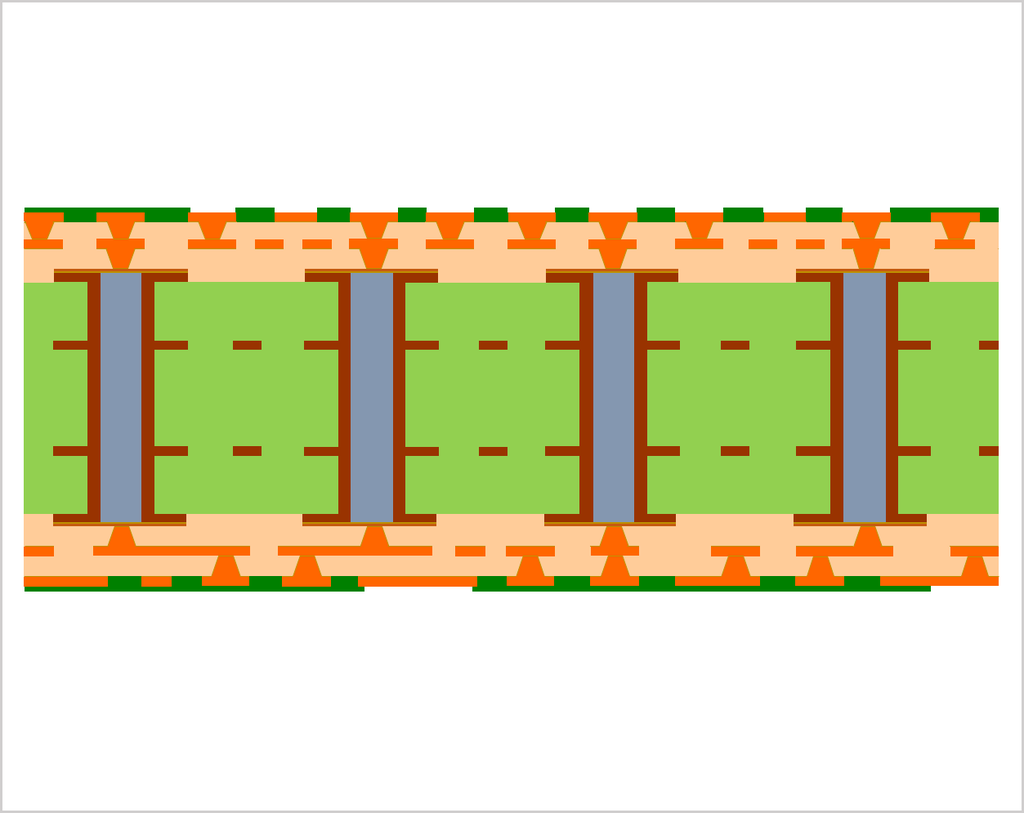

最外層をスルーホールめっきした状態の材料を黒化処理などで表面粗化し、穴埋め法(Hole Plugging Process)と呼ばれる方法でスルーホール内に熱硬化性の穴埋めインクを充てん、穴埋めします。充てん後、乾燥し、表裏にはみ出した余分なインクを削り取った後に、完全硬化させます。

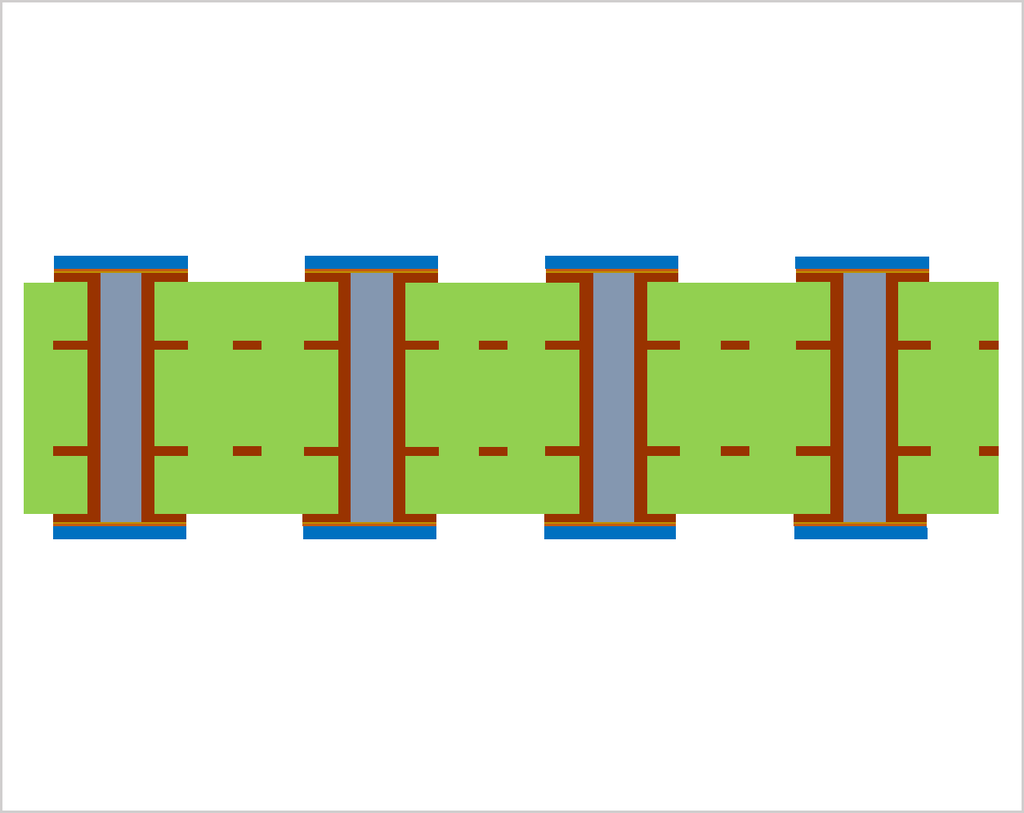

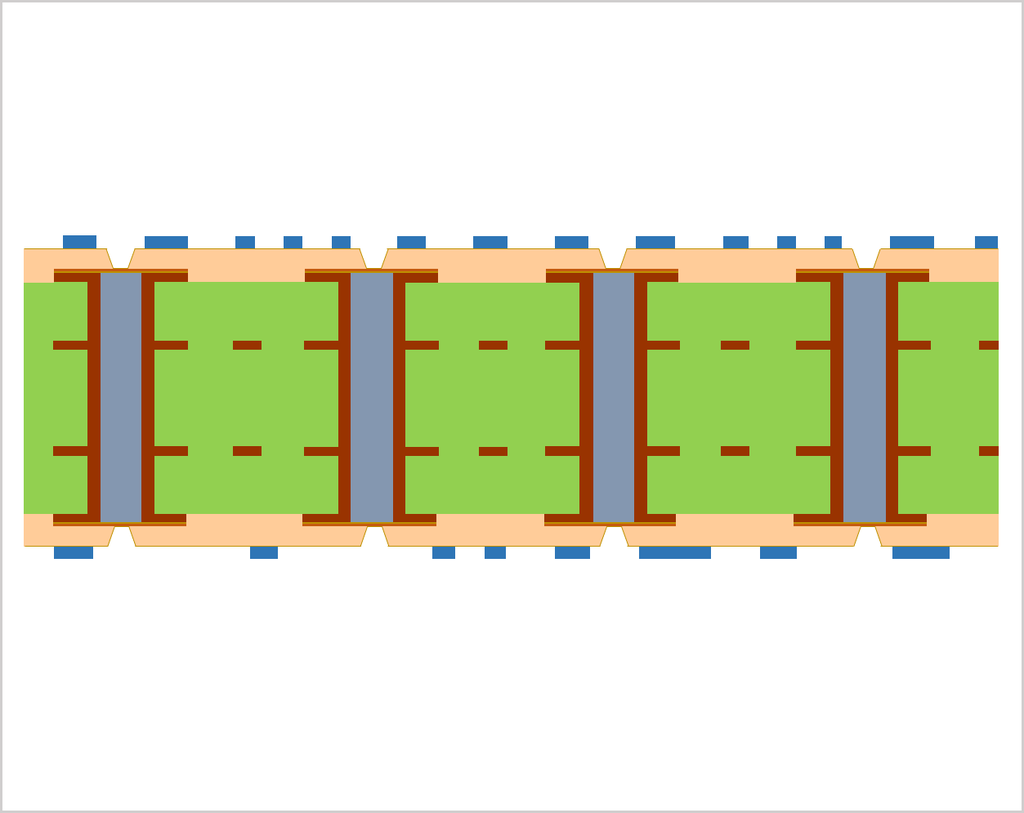

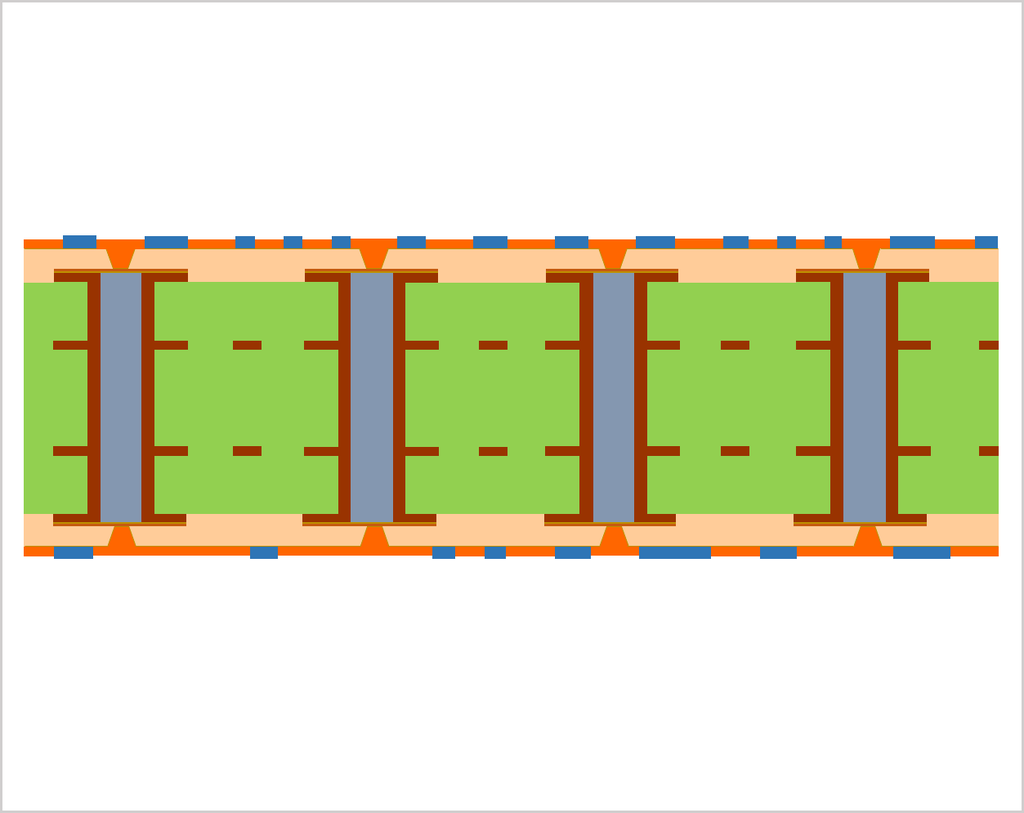

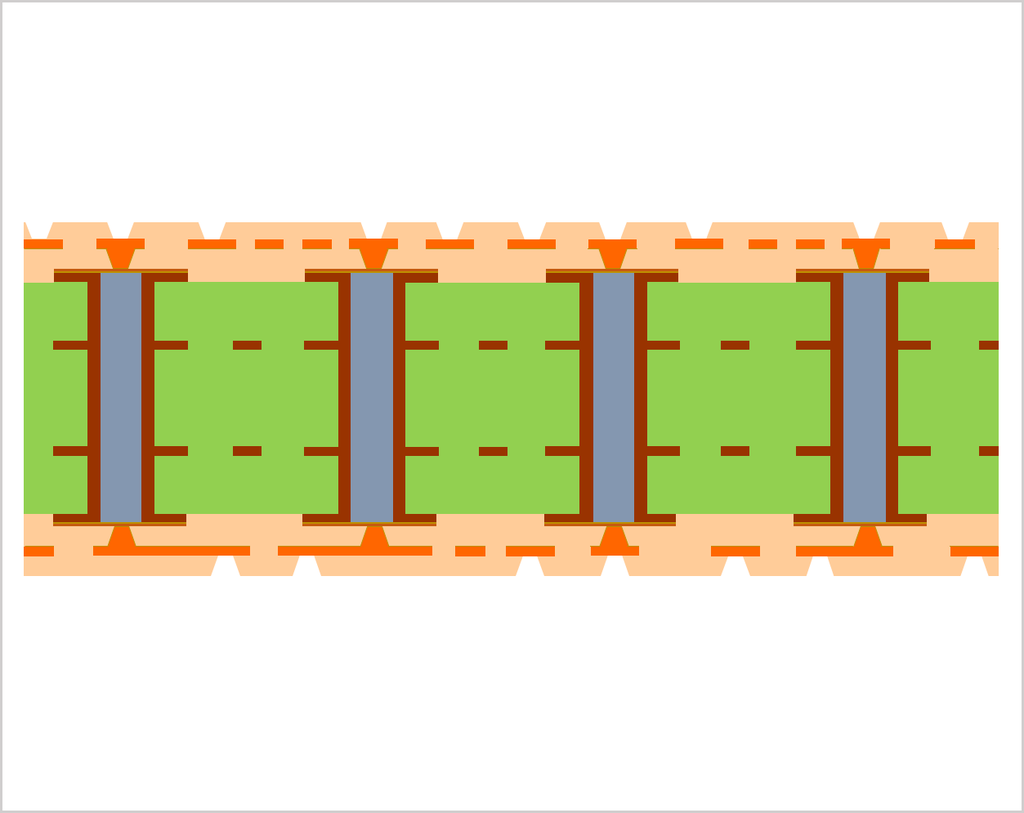

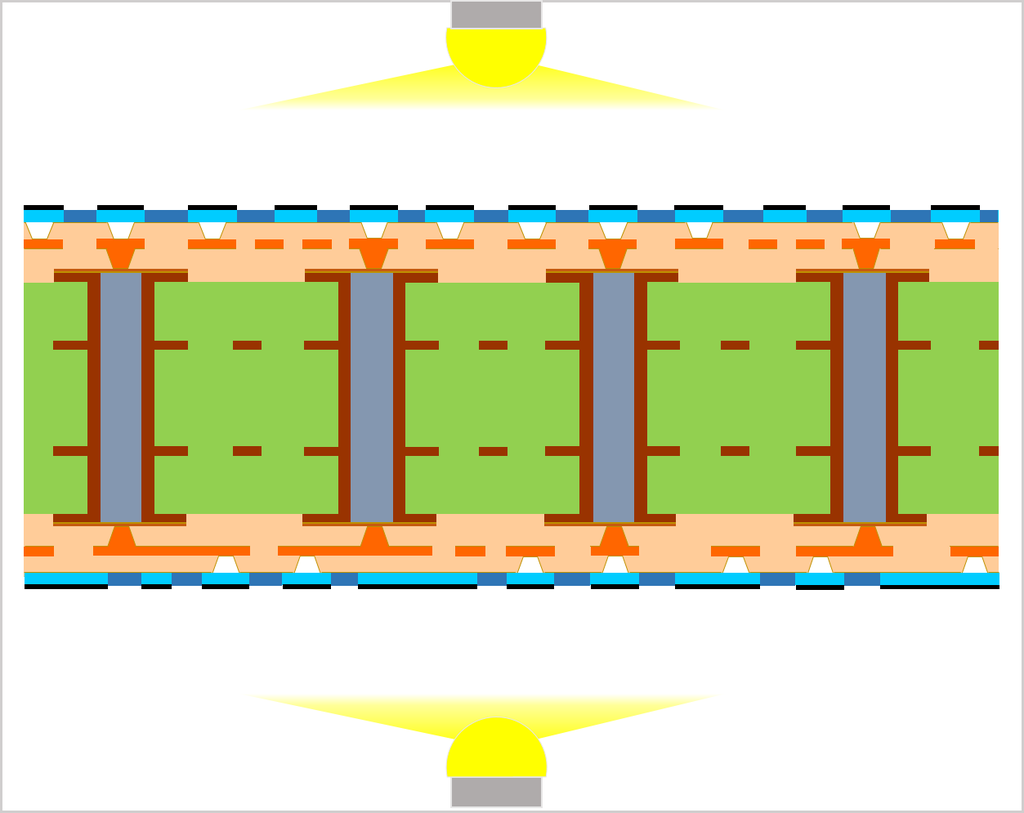

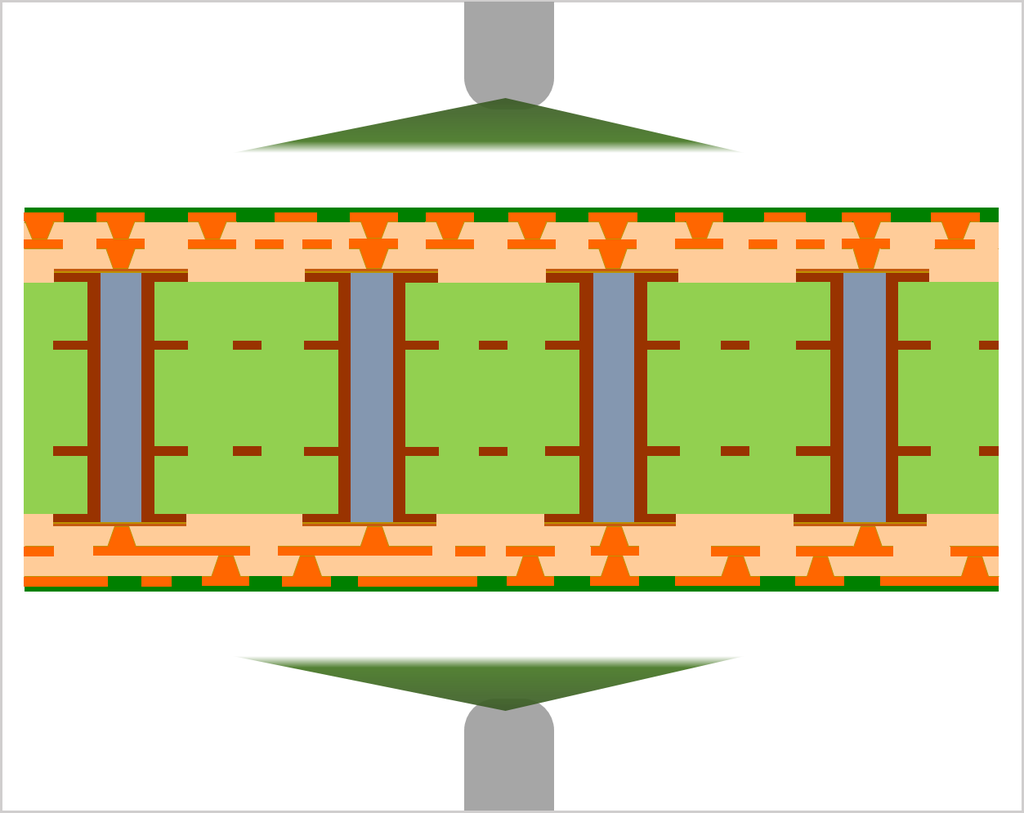

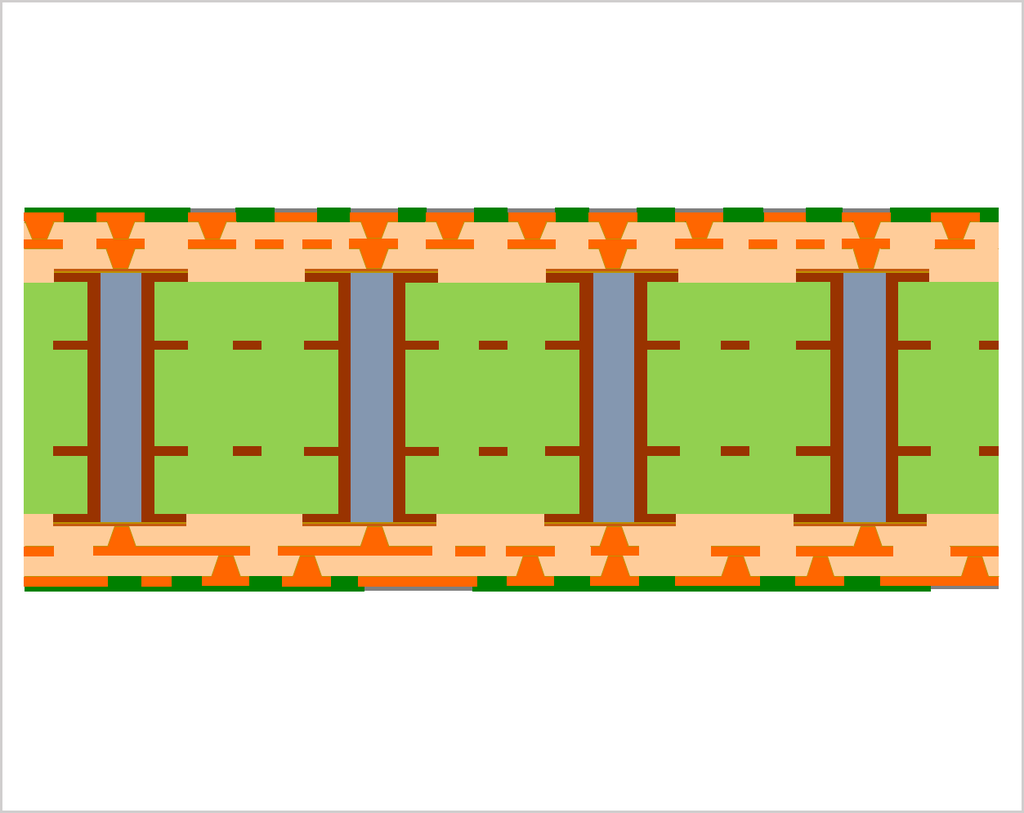

穴埋めの替わりに電気銅めっきでスルーホールフィリングすることで、穴埋めに加えて後工程の無電解銅めっきが不要となり、さらに放熱性が向上するために、一部で実用化されています。当社ではトップルチナLTFなどをラインナップしています。